# Introduction to GPU "Low-level" Programming

How does that even work?

Thomas Applencourt (apl@anl.gov) July 31, 2023

- "If it's simple, it's always false. If it's not, it's unusable." Paul Valéry

- "Trust, but verify" Russian proverb

- And sorry in advance for the 3h long lecture...<sup>1</sup>

<sup>1</sup>"Stay awhile and listen..." Deckard Cain

#### 1. Introduction

- 2. Programming Model API / Runtime

- 3. Kernel Language / Compilation

- 4. Bonus: And where the fun begins

- 5. Conclusion

# Introduction

- Part of the Performance Engineer Group at Argonne<sup>2</sup>

- $\cdot\,$  Main focus on Aurora Compiler and Runtime

- So Expertise in Intel Toolchain, the rest will be more hand-wavy...<sup>3</sup>

- Member of the SYCL committee

<sup>&</sup>lt;sup>3</sup>I'm sure some people in the audience will be able to answers any AMD/NVIDIA question

<sup>&</sup>lt;sup>2</sup>Like Vitali and Servesh

- Teach you CUDA, Hip, Level Zero<sup>4</sup>

- You are all smart, if you need to learn it you can find super nice tutorial online

<sup>&</sup>lt;sup>4</sup>But maybe I will teach you some OpenCL...

- Give you some foundation to understand the difference and similitude between multiple low-level programming models ("Any fool can know. The point is to understand." Ernest Kinoy)

- Make clear the layering approach of current toolchains

#### One big question

• Why one "need" to use CUDA for NVIDIA hardware, Hip for AMD, and L0 for Intel?<sup>5</sup>

(a) Level Zero

(c) HIP

<sup>5</sup>But then how can OpenCL be portable?

- Programming Model / Runtime<sup>6</sup>

- Kernel Language, and Kernel Execution

<sup>&</sup>lt;sup>6</sup>This is the only thing who matter, this rest is trivial

# Programming Model API / Runtime

# Programming Model API / Runtime

**Runtime and Runtimes**

#### A runtime is a implementation of a programming language's execution model

#### "All problems in computer science can be solved by another level of indirection" David Wheeler

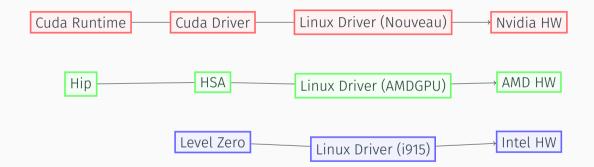

- The Linux Drivers are the "lower-level" we will discuss. Huge effort to implement.<sup>7</sup>

- The level on top (CUDA Driver, HSA, Level Zero) abstracts away a little bit more of the hardware, but still provides a lot of control <sup>8</sup>

- The last level ( Cuda Runtime, HIP) are "fully" hardware independent

<sup>7</sup>See nice blog post about the Linux M4 drivers <sup>8</sup>Sweet spot to write higher-lever runtime

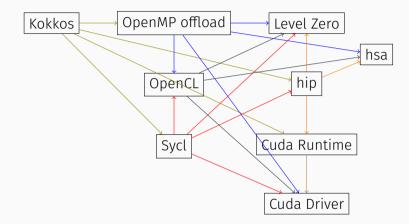

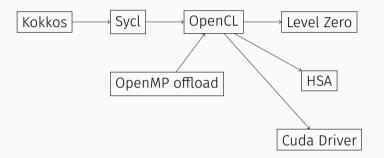

#### Taking about higher-level Programming model

- OpenCL -> \*9

- OpenMP Offload -> HSA

- Kokkos -> Cuda Runtime -> Cuda Driver

- HIP -> L0<sup>10</sup>

<sup>10</sup>Maybe more surprising, we will talk about this more at the end

<sup>&</sup>lt;sup>9</sup>Yes, I Like OpenCL... Soon you will too!

- In short we have a "High Level" programming model. Used by Application.

- $\cdot$  A "low-level" programming model that the high-level runtime is written with

- Each layer of abstraction is a trade-off between flexibility/performance and convenience/productivity

All of this is **relative** to who you are talking with.

- No technical reason for having so much "intermediate" programming model

hipcc was a perl script that did 's/cu/hip/g' to avoid copyright infringement<sup>11</sup>

- Always hard to have a standard (\*insert XKCD\*)

- OpenCL is the standard, but low-adoption by vendors

- Please don't let vendors make the same mistake with new ML accelerators!

<sup>&</sup>lt;sup>11</sup>Not a lawyer, but the "recent" supreme court Google vs Oracle may help

Hip and Cuda Runtime should not be used anymore.

- $\cdot$  Too low-level for Application who want to use nice C++ construct<sup>12</sup>

- Too high-level for people who have advance use-cases.

Kokkos, Sycl OpenMPOffload already bypass HIP / CUDA runtime, so no "overhead" by using those programming models

<sup>&</sup>lt;sup>12</sup>Come on, who wants to cast the output of malloc...

You are young and not yet totally jaded, so I share my dream with you!

# Programming Model API / Runtime

Main concepts (shared)

Pointer Everywhere (output is the return error code, Cuda Driver Example)<sup>13</sup>

- 1 int count;

- 2 err = cuDeviceGetCount(&count);

API can be called twice (OpenCL Example, similar in L0)

- 1 // Get number of platorm

- 2 cl\_uint platformCount;

- 3 clGetPlatformIDs(0, NULL, &platformCount);

- 4 cl\_platform\_id\* platforms = (cl\_platform\_id\*) malloc(sizeof(cl\_platform\_id) \*

- $\hookrightarrow$  platformCount);

- 5 // Populate the newly allocated array

- 6 errr = clGetPlatformIDs(platformCount, platforms, NULL);

<sup>13</sup>cu\* == cuda driver, cuda\* == cuda runtime.

#### And Pointer of Pointer, and strut!

In C, malloc return a null pointer when it fail. Not in cuda!

1 CUresult cuMemAllocHost ( void\*\* pp, size\_t bytesize )

Some API use struct to avoid 200 parameters

```

ze command queue desc t commandQueueDesc = {

ZE STRUCTURE TYPE COMMAND QUEUE DESC.

\mathbf{2}

3

NULL.

computeQueueGroupOrdinal.

0. // index

5

0. // flags

6

ZE COMMAND QUEUE MODE DEFAULT.

7

ZE COMMAND QUEUE PRIORITY NORMAL

8

};

9

ze_command_queue_handle_t hCommandQueue;

10

errno = zeCommandQueueCreate(hContext, hDevice,

11

&commandOueueDesc. &hCommandOueue):

12

```

- Find devices, load your kernels

- Allocate GPU Memory

- Transfer Memory: From and To the device

- Execute your commands

Not that hard!

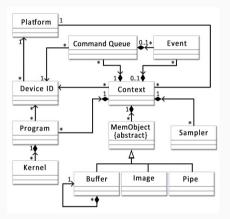

### A picture is Worth a Thousand Words $^{\rm 15}$

- $\cdot$  OpenCL view of the world <sup>14</sup>

- All other programming models are roughly the same

- (Please ignore MemObject and Sampler)

<sup>14</sup>Picture from the OpenCL Doc

<sup>15</sup>Maybe more when it's a UML diagram

Platform: a collection of Device sharing some property

```

cl int clGetPlatformIDs( cl uint num entries.

1

cl platform id* platforms.

\mathbf{2}

cl uint* num platforms);

3

ze result t zeDriverGet(uint32 t *pCount.

5

ze driver handle t *phDrivers)

6

7

8

CUresult cuDeviceGetCount ( int* count )

CUresult cuDeviceGet ( CUdevice* device. int ordinal)

9

10

% Alwavs fun to change the naming convension

11

cudaError t cudaGetDeviceCount ( int * count )

12

cudaError t cudaGetDevice ( int* device )

13

```

- Devices are bound to a Context

- The context holds all the management data to control and use the device.

```

1 % One Device

2 CUresult cuCtxCreate_v3 ( CUcontext* pctx, CUexecAffinityParam* paramsArray,

3 int numParams, unsigned int flags, CUdevice dev )

4 % All the Device in the Platform

5 ze_result_t zeContextCreate(ze_driver_handle_t hDriver,

6 const ze_context_desc_t *desc,

7 ze_context_handle_t *phContext)

```

For example in L0, it's forbidden to exchange memory between different contexts (whether they share the same device or not)<sup>16</sup>

• Any "advanced" use cases (multi-device, multi-process, interface with other library) need to be aware of context.

<sup>&</sup>lt;sup>16</sup>I think it's the same in CUDA...

# Note on CUDA: contexts are one of the major differences between runtime and driver APIs

- $\cdot$  CUDA driver is a state machine. You pop and push context on a stack

- 1 CUresult cuCtxSetCurrent ( CUcontext ctx )

- And are not exposed to the runtime API (uses an implicit primary context). So be careful!

[...] for example, because if all plug-ins run in the same process, they will all share a context but will likely have no way to communicate with each other. So, if one of them calls cudaDeviceReset() after finishing all its CUDA work, the other plug-ins will fail because the context they were using was destroyed without their knowledge. <sup>17</sup>

//docs.nvidia.com/cuda/cuda-runtime-api/driver-vs-runtime-api.html

<sup>&</sup>lt;sup>17</sup>https:

Submit "command" to queue/stream. Commands can be

- Memory Copy

- Kernel Submission

- Synchronization

- ...

#### Differences between programming models

- In LO, queues are out-of-order<sup>18</sup>

- In CUDA runtime and driver and HIP, streams are in-order<sup>19</sup>

- In OpenCL, they can be both

- In HSA, it's a ring buffer of packets

- Out-of-order queues can be a source of error  $^{20}$

<sup>18</sup>Just checked, the latest L0 version we know have a ZE\_COMMAND\_QUEUE\_FLAG\_IN\_ORDER flags.

<sup>19</sup>For more complex use cases, use cuda-graph

<sup>20</sup>But are powerful, will see later

#### **Command Submission**

Commands can be submitted Asynchronously or in blocking manner

```

CUresult cuMemcpy ( CUdeviceptr dst, CUdeviceptr src,

size t ByteCount ) % Where is my stream?!

2

CUresult cuMemcpvAsvnc ( CUdeviceptr dst, CUdeviceptr src, size t ByteCount,

3

\hookrightarrow CUstream hStream )

4

cl int clEnqueueSVMMemcpy(

5

cl command queue command queue.

6

cl bool blocking copy,

7

void* dst ptr.

8

const void* src ptr.

9

size t size,

10

cl uint num events in wait list,

11

const cl event* event wait list,

12

cl event* event):

13

```

• Async is a common source of error

If it's asynchronous you need to synchronize

- via Event (specify dependencies for fine grained synchronization)

- via Barrier (for coarse synchronization)

4

#### OpenCL, L0<sup>21</sup>:

- 1 zeCommandListAppendMemoryCopy(..., &e1) // e1 will be signaled at completion

- 2 zeCommandListAppendMemoryCopy(..., &e2) // e2 will be signaled at completion

- 3 ze\_event\_t depend\_in [2] {e1,e2};

- 5 zeCommandListAppendMemoryCopy(..., 2, depend\_in, &e3) // Inputs and output

- 6 zeEventHostSynchronize(e)

- 1 hipMemcpyAsync // Hip, Cuda have optional Async, default blocking

- 2 hipEventRecord

- 3 hipEventSynchronize

(for more fancy use cases, use cuda-graph)

<sup>21</sup>So elegant

#### Wait on queue / stream (wait until all the work has been done)

- 1 *zeCommandQueueSynchronize*

- 2 cudaStreamSynchronize

- 3 cudaDeviceSynchronize % Whoa?

Coarse grain. Use with caution.

# Programming Model API / Runtime

Memory Allocation

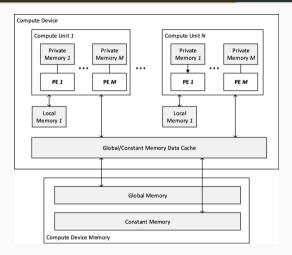

## Types of GPU Memory<sup>25</sup>

- Device Memory: Accessible only on the particular device<sup>22</sup>

- Shared Memory: Accessible by both the host and the device<sup>23</sup>

- This may impact performance, Different migration strategies

- Can be migrated via prefetching<sup>24</sup>

- Host memory

- "Pinned" memory. CPU memory but has been registered by the runtime.

- May required for some optimizations / performance

- Malloc-ed Memory

<sup>22</sup>Read the documentation to know if it's accessible by OTHER devices. Context, wink, wink

<sup>23</sup>Nvidia calls it "Managed"

<sup>24</sup>Do not confuse with prefetch of memory inside a kernel

<sup>25</sup>OpenCL has buffer, but lets not go that way...

- Doesn't matter,

- NUMA is bad, Locality is good.

- Please don't use shared everywhere...

- Wrong data-transfer is the number one bug when doing GPU programming.

- Start with shared-allocation, then trace/profile and optimize<sup>26</sup>

- Premature Optimization is the root of all evil, but not profiling is eviler!

<sup>&</sup>lt;sup>26</sup>SYCL has a nice buffer/accessors to solve the data-transfer problem

Allocates size bytes of host memory that is page-locked and accessible to the device. The driver tracks the virtual memory ranges allocated with this function and automatically accelerates calls to functions such as cudaMemcpy(). Since the memory can be accessed directly by the device, it can be read or written with much higher bandwidth than pageable memory obtained with functions such as malloc(). Allocating excessive amounts of pinned memory available to the system for paging.<sup>27</sup>

<sup>27</sup> https://docs.nvidia.com/cuda/cuda-runtime-api/group\_\_CUDART\_\_MEMORY.htm

- $\cdot\,$  All data fit on the GPU

- $\cdot$  move everything over

- $\cdot$  do a ton of computation

- move back

You should aim for thim. If you cannot, we will discuss other strategies latter.<sup>28</sup>. **Memory transfers are expensive. Don't do it!** Or at least try...

<sup>&</sup>lt;sup>28</sup>Please not that it's the same in CPU. Keep data in cache

# Programming Model API / Runtime

**Kernel Submission**

Magic / Syntactic sugar<sup>29</sup>

1 mykernel<<<blocks, threads, shared\_mem, stream>>>(args);

But just call HSA / Cuda Driver behind the scenes.

<sup>&</sup>lt;sup>29</sup>Haha, no lambda. Haha, new non C syntax...

#### behind the seen: OpenCL Cuda

| 1  | <pre>cl_int clEnqueueNDRangeKernel(cl_command_queue command_queue,</pre> |

|----|--------------------------------------------------------------------------|

| 2  | cl_kernel kernel,                                                        |

| 3  | cl_uint work_dim,                                                        |

| 4  | <pre>const size_t *global_work_offset,</pre>                             |

| 5  | <pre>const size_t *global_work_size,</pre>                               |

| 6  | <pre>const size_t *local_work_size,</pre>                                |

| 7  | cl_uint num_events_in_wait_list,                                         |

| 8  | <pre>const cl_event *event_wait_list,</pre>                              |

| 9  | cl_event *event)                                                         |

| 10 |                                                                          |

| 11 | CUresult cuLaunchKernel ( CUfunction f, unsigned int gridDimX, uns       |

CUresult cuLaunchKernel ( CUfunction f, unsigned int gridDimX, unsigned int  $\hookrightarrow$  gridDimY, unsigned int gridDimZ, unsigned int blockDimX, unsigned int  $\hookrightarrow$  blockDimY, unsigned int blockDimZ, unsigned int sharedMemBytes, CUstream

→ hStream, void\*\* kernelParams, void\*\* extra )

```

1

% Similar in LO, Count versus Size, and by kernel

2

zeKernelSetGroupSize(hKernel, groupSizeX. 1. 1):

3

ze group count t groupCount = { numGroupsX, 1, 1 };

4

zeCommandListAppendLaunchKernel(hCommandList, hKernel, &groupCount, NULL, 0,

5

\rightarrow NULL):

6

% HSA Werited you get a packet from queue and then signaling, but still same idea

7

typedef struct hsa kernel dispatch packet s { uint16 t header ;

8

uint16 t setup;

9

uint16_t workgroup_size_x ; uint16_t workgroup_size_y ; uint16_t workgroup_size_z;

10

\rightarrow uint16 t reserved0:

11

uint32 t grid size x ;

uint32_t grid_size_y ;

12

uint32 t grid size z:

13

uint32_t private_segment_size; uint32_t group_segment_size;

14

15

```

#### Launching Kernel

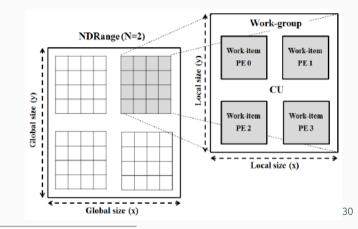

<sup>30</sup>From "Design of OpenCL Framework for Embedded Multi-core Processors"

- $\cdot\,$  Your code was split between hosts and GPU code

- Your kernels need to loaded by the GPU runtime!

- 1 clCreateProgramWithSource

- 2 clCreateProgramWithIL

- 3 clCreateProgramWithBinary

- 4 zeModuleCreate ( ZE\_MODULE\_FORMAT\_IL\_SPIRV | ZE\_MODULE\_FORMAT\_NATIVE)

- 5 cuModuleLoad

# Programming Model API / Runtime

Wrapping Up: Going thought an OpenCL Example

• "Low-level" Code ( I will guess that cuda-driver will be similar, L0 more verbose, and HSA ever more)

#### Load Platform and Device

```

cl uint platform idx = (cl uint) atoi(argv[1]);

1

cl uint device idx = (cl uint) atoi(argv[2]);

\mathbf{2}

3

clGetPlatformIDs(0, NULL, &platform count);

4

5

cl platform id* platforms = (cl platform id*)malloc(sizeof(cl platform id) *

6

\rightarrow platform count):

clGetPlatformIDs(platform count, platforms, NULL);

\overline{7}

8

cl platform id platform = platforms[platform idx];

9

10

cl uint device_count;

11

clGetDeviceIDs(platform, CL_DEVICE_TYPE_ALL , 0, NULL, &device_count);

12

13

cl device id* devices = (cl device id*)malloc(sizeof(cl device id) *

14

\leftrightarrow device count):

clGetDeviceIDs(platform, CL_DEVICE_TYPE_ALL , device_count, devices, NULL);

15

16

cl device id device = devices[device idx]:

17

```

- 1 // A context is a platform with a set of available devices for that platform.

- 3 cl\_command\_queue queue = clCreateCommandQueue(context, device,

- $\hookrightarrow$  CL\_QUEUE\_PROFILING\_ENABLE, &err);

- // Create the program

- 5 cl\_program program = clCreateProgramWithSource(context, 1, &kernelstring,

- $\hookrightarrow$  NULL, Serr);

- 6 clBuildProgram(program, device\_count, devices, "", NULL, NULL);

- 7 cl\_kernel kernel = clCreateKernel(program, "hello\_world", &err);

4

```

#define WORK DIM 1

size t global0 = (size t) atoi(argv[3]);

\mathbf{2}

const size t global[WORK DIM] = { global0 };

3

size t local0 = (size t) atoi(argv[4]);

4

const size t local[WORK DIM] = { local0 }:

5

% No vent

6

clEnqueueNDRangeKernel(queue, kernel, WORK DIM, NULL,

7

global, local, 0, NULL, NULL);

8

clFinish(queue):

9

```

## Programming Model API / Runtime

Notes on Performance

- $\cdot$  You want to keep the GPU busy

- When the GPU is computing something, the CPU should start preparing the next batch of work

- Importance of asynchronously

Async: [OpenMP][AMDGPU] Switch host-device memory copy to asynchronous version (real thing: *https://reviews.llvm.org/D115279*)

#### Overlapping is Key to good performance

- PCI is damn slow!<sup>31</sup>

- PCI 64 GB/s (unidirectional)

- HBM 410 GB/s

- GPU 50 TFlops+

- Recompute is better than to load

- Overlap compute and data-transfers

- PCI is bidirectional so please do H2D and D2H at the same time!

- Avoid over-synchronization!

<sup>&</sup>lt;sup>31</sup>And for integrated architectures, you have NUMA so same things... Data-movement will always be more expensive than compute

Importance of asynchronously!<sup>32</sup>

- Submit kernels to multiple stream / queue

- Submit kernels to an out-of-order queue.

<sup>32</sup>Or use multiple thread / process but this is cheating

|                   | zeEventHostSynchro | zeEventHostSynchronize |                            |  | zeEventHostSynchronize |  |                            |  |

|-------------------|--------------------|------------------------|----------------------------|--|------------------------|--|----------------------------|--|

| Juid 1            |                    |                        |                            |  |                        |  |                            |  |

| 0815  <br>081   u |                    |                        |                            |  |                        |  |                            |  |

|                   | zeMemoryCopy(DH)   | zeMemoryCopy(HD)       | zeMemoryCopy(DH)           |  | zeMemoryCopy(HD)       |  | zeMemoryCopy(DH)           |  |

|                   | zeCommandListAppen |                        | zeCommandListAppendBarrier |  |                        |  | zeCommandListAppendBarrier |  |

| 0767949           |                    |                        |                            |  |                        |  |                            |  |

| ze ze    | ze ze zeCommandQueueSynchronize                             |          | ze ze zeCommandQueueSynchronize                         |         | ze z zeCommandQueueSynchronize                            |           | ze zeCommandQueueSynchronize                              |  |  |

|----------|-------------------------------------------------------------|----------|---------------------------------------------------------|---------|-----------------------------------------------------------|-----------|-----------------------------------------------------------|--|--|

|          |                                                             |          |                                                         |         |                                                           |           |                                                           |  |  |

|          |                                                             |          |                                                         |         |                                                           |           |                                                           |  |  |

|          |                                                             |          |                                                         |         |                                                           |           |                                                           |  |  |

|          |                                                             |          |                                                         |         |                                                           |           |                                                           |  |  |

| _ZTSZ5be | enchlfESt4pairllSt6vectorllSallEEENSt7_<br>zeMemoryCopy(MD) | ZTSZ5ben | chifESt4pairllSt6vectorllSallEEENSt<br>zeMemoryCopy(MD) | ZTSZ5be | nchifESt4pairilSt6vectorilSallEEENSt7<br>zeMemoryCopy(MD) | _ZTSZ5ber | nchlfESt4pairllSt6vectorllSallEEENSt7<br>zeMemoryCopy(MD) |  |  |

- You see, all the same. And lot of Bridge betweem them!

- Context, Queue, Execution Space, synchronize

- Some are less verbose more high level (HIP/CUDA runtime) but you loose some flexibility<sup>33</sup>

- IMO HIP/CUDA runtime are in a weird intermediate level.

<sup>&</sup>lt;sup>33</sup>And need to deal with some state-machine...

Real Time Experience (controversial)

- Experience: The runtime performance is far more important than the kernel performance

- Improving Kernel performance will give you a few percent; doing too much data-tranfer will slowdown you code 100x.

# Kernel Language / Compilation

## Kernel Language / Compilation

Compilation

- The GPU code needs to be loaded!

- Let's see how they are compiled

#### Compiling: At the beginning

#### How to write GPU programming

```

1 % Cuda HIP

2 __global__ void cuda_hello(){

3 printf("Hello World from GPU!\n");

4 }

5 % OpenCL

6 __kernel void hello_world() {"

7 printf("Hello World from GPU!\n");

8 };

```

#### So much difference!

- What can you put in device code has limitation depending on the Hardware / Compiler

- No dynamic allocation, No throw, No recursion, No virtual Functions, ...

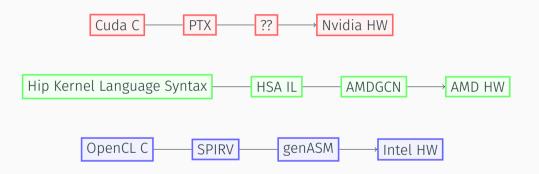

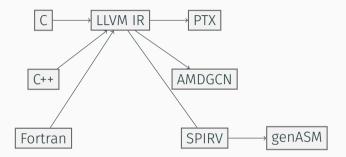

### Compiling: A little more

(Note that GCC bypass LLVM IR to generate PTX and AMDGCN <sup>34</sup>)

<sup>&</sup>lt;sup>34</sup>or nobody generate AMDGCN and everybody HIP IL, not clear...

```

1 #pragam omp target

2 printf("Hello World!\n");

3

4 // Lambda

```

```

5 Q.single_task([] {printf(Hello World![n");}}.wait();

```

Ask yourself how can you implement this, what "low-level" call you need? We will see it in the Bonus part!

## Kernel Language / Compilation

Kernel Language: GPU programming 101

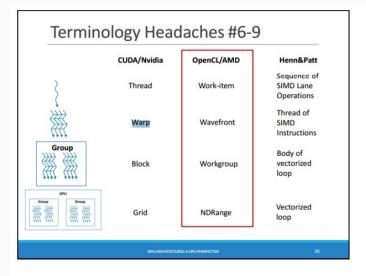

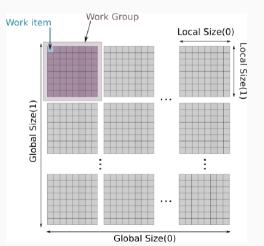

#### Terminology: Credit Derek Hower

- $\cdot\,$  Just think of the GPU as a CPU with lots of threads executing SIMD instruction

- GPU programs are pretty boring:

- $\cdot\,$  Use Shared Local Memory  $^{35}$  when possible to not read from the Main Memory

- Be careful of register pressure

- "Nothing Special"<sup>36</sup>

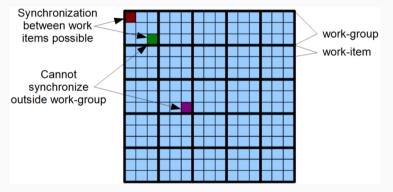

- GPU are fast because they force you to NOT synchronize between threads that live in difference work-group. Freedom versus Performance.

<sup>35</sup>Shared Memory in cuda

<sup>36</sup>"coalescing memory" == Don't do random access...

## Not about branching (don't want to displease Nvida people)

- In SIMD, conditional are implemented as masking, and then execute both branch<sup>37</sup>

- Same in GPU, But Some GPU have some "thread divergence" capability<sup>38</sup> Volta independent thread scheduling enables interleaved execution of statements from divergent branches. This enables execution of fine-grain parallel algorithms where threads within a warp may synchronize and communicate.

<sup>&</sup>lt;sup>37</sup>Both branch if both branch are needed. This is why is better to sort your data... <sup>38</sup>After votla for Nvidia

## Synchronization Possibilities

From An Introduction to the OpenCL Programming Model by Jonathan A. Thompson

Index space

From "An Introduction to the OpenCL Programming Model" by Jonathan A. Thompson

- Progress Forward guarantees are complicated...

- I really don't want to open this can of worms.

- Advice: Please don't use atomic to synchronize

- For an overview of the fun see: *TowardsAlignmentofParallelisminSYCLandISOC++* by John Pennycook

- $\cdot$  GPUs do not have the same ISA as CPU, so two compilation phases

- GPU are fast because they are stupid, and they are just a big SIMD 10k threads CPU

- Lots of good tutorials online for GPU Kernel Programming

High Level versus Low-level: Interoperability

- Maybe, Maybe not

- Depends on your usage

- $\cdot$  Depends on the quality of the runtime

- IMO Cuda Runtime is at the same level as SYCL

- Don't be afraid of the runtime

- They have bugs and performance bugs<sup>39</sup>

- Please benchmark, trace, and report

- If you find bugs, just use interopts!

<sup>&</sup>lt;sup>39</sup>But maybe less than your code, just because more people use them...

All (at least I hope so) "high-level" can (SHOULD!) should interoperate with some low-level runtime.

```

#OpenMP interop with L0

1

omp interop t interop;

2

#pragma omp interop device(id) , targetsync : o)

3

auto hPlatform = static cast<ze driver handle t>(

omp_get_interop_ptr(o, omp_ipr_platform, &err)

5

);

6

7

#Sycl interopt with CUDA

8

cuStream T s = get native<backend::cuda>(Q);

9

```

Best of both worlds

- Use high-level by default

- $\cdot$  Go down when required

Tracer: How to?

- $\cdot\,$  Tracing the runtime is mandatory to understand what is going one

- And it's fun. Like the satisfaction of putting clarity in life full of chaos

- Does Cuda Runtime "foo«»" really call cuda driver "Launch Kernel"?

- Does memcopy use Copy Engine or Compute kernel?

- Why is my code is slow after my 1M gpu device alloc?

- Dump Arguments and timestamp before and after the call

- Provide some analysis tools

- 1 clEnqueueMemcpyINTEL\_entry:

- 2 { command\_queue: 0x181a540, blocking: CL\_FALSE,

- 3 dst\_ptr: 0xffffc001ffd80000, src\_ptr: 0x00007f5b20088280, size: 64,

```

→ num_events_in_wait_list: 0,

```

- 4 event\_wait\_list: 0x0, event: 0x7ffc4ac01378, event\_wait\_list\_vals: [] }

5 clEnqueueMemcpyINTEL\_exit:

- 6 { errcode\_ret\_val: CL\_SUCCESS, event\_val: 0x1dffb30 }

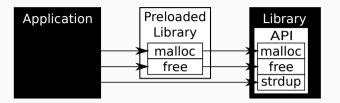

- But How to intercept API call?

- Some APIs provide Callback

- You can always write you own intercept layers!

Famous Example: Inte's Intercept Layer for OpenCL Applications https://github.com/intel/opencl-intercept-layer

Nice explanation by Rafal Cieslak https://rafalcieslak.wordpress.com/ 2013/04/02/dynamic-linker-tricks-using-ld\_ preload-to-cheat-inject-features-and-investigate-programs/

Please replace rand by some some of your favorite API calls

```

% cat main.cc

1

#include <stdio.h>

2

#include <stdlib.h>

3

int main(){

4

printf("%d\n",rand()%100);

\mathbf{5}

6

$ gcc -shared -fPIC inspect rand.c -o inspect rand.so -ldl

7

$ ./a.out

8

9

42

```

How can we intercept this call?

#### PRELOAD + dlopen = <3

```

$ cat inspect rand.c

1

#define GNU SOURCE

\mathbf{2}

#include <dlfcn.h>

3

#include <stdio.h>

4

typedef int (*rand)(void);

5

int rand(void)

6

7

printf("Rand_begin");

8

orig rand f type orig rand;

9

orig_rand = (orig_rand_f_type)dlsym(RTLD_NEXT, "open");

10

int o = orig rand();

11

printf("Rand end");

12

return o;

13

14

$ gcc -shared -fPIC inspect rand.c -o inspect rand.so -ldl

15

$ LD PRELOAD=$PWD/inspect rand.so ./a.out

16

Rand_begin

17

99

18

```

- Of course, a little more complicated in real life, but this is what some tools are doing. For example THAPI/iprof that we will show later

- But more and more APIs provide a clean callback mechanism

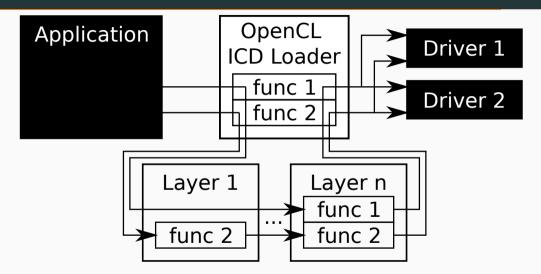

#### The clean way: Loader

#### **OpenCL Example**

https://github.com/Kerilk/OpenCL-Layers-Tutorial

```

static CL API ENTRY cl int CL API CALL clGetPlatformIDs wrap(

1

cl uint num entries.

2

cl platform id* platforms.

3

cl uint* num platforms) {

fprintf(stderr, "clGetPlatformIDs(num entries: %d)\n", num entries);

5

cl int res = tdispatch->clGetPlatformIDs(num entries, platforms, num platforms);

6

if (res == CL SUCCESS && num platforms)

7

fprintf(stderr. ". *num platforms: %d\n". *num platforms):

8

return res:

9

10

11

static void init dispatch() {

12

dispatch.clGetPlatformIDs = &clGetPlatformIDs wrap:

13

14

```

And then just put this library and your path, and your tada.

Tracer Example: THAPI

- At the beginning no tracer for Level Zero

- Still not one common tracer for low-level-programming

- So we wrote one!

- THAPI Support: Cuda Runtime, Cuda Driver, HIP, LO, OpenCL, OpenMP-T

#### Fabulous tool: Trace

```

> ./iprof -t ./a.out

1

\mathbf{2}

{ thread type: ompt thread initial, thread data: 0x00007f5b0cf0ac48 }

ompt callback target:

3

{ kind: ompt target. endpoint: ompt scope end. device num: 0. task data: 0x0000000000000000.

4

target id: 1. codeptr ra: 0x00007f5b26fa47e0

5

6

[...]

7

ompt callback target data op intel:

8

{ endpoint: ompt scope begin, target id: 1, host op id: 7, optype:

\hookrightarrow ompt target data transfer to device.

src addr: 0x00007f5b20088280. src device num: -10. dest addr: 0xffffc001ffd80000.

9

10

dest device num: 0. bytes: 131072. codeptr ra: 0x00007f5b26fa47e0 }

11

clEnqueueMemcpvINTEL entry:

12

{ command queue: 0x181a540, blocking: CL FALSE.

13

dst ptr: 0xffffc001ffd80000. src ptr: 0x00007f5b20088280. size: 64. num events in wait list: 0.

event wait list: 0x0. event: 0x7ffc4ac01378. event wait list vals: [] }

14

15

clEnqueueMemcpvINTEL exit:

{ errcode ret val: CL SUCCESS, event val: 0x1dffb30 }

16

ompt callback target data op intel:

17

{ endpoint: ompt_scope_end, target_id: 1, host_op_id: 7, optype:

18

\hookrightarrow ompt target data transfer to device.

19

src addr: 0x00007f5b20088280. src device num: -10. dest addr: 0xffffc001ffd80000.

20

dest device num: 0. bytes: 131072. codeptr ra: 0x00007f5b26fa47e0

```

## Tally

```

$iprof ./target teams distribute parallel do.out # Using Level0 backend of OpenMP

1

2

Trace location: /home/tapplencourt/lttng-traces/iprof-20210408-204629

3

BACKEND OMP | 1 Hostnames | 1 Processes | 1 Threads |

4

Name |

Time | Time(%) | Calls | Average |

Min |

Max

5

ompt target | 3.65ms | 100.00% |

1 | 3.65ms | 3.65ms | 3.65ms |

6

Total | 3.65ms | 100.00% |

1 1

7

8

BACKEND OMP TARGET OPERATIONS | 1 Hostnames | 1 Processes | 1 Threads |

9

Name I

Time |

Time(%) | Calls |

Average |

Min |

Max

10

ompt target data alloc /

1.97ms |

54.19% I

4 | 491.63us |

847ns |

1.12ms

11

ompt target data transfer to device | 1.26ms |

34.63% |

5 | 251.37us | 112.60us |

460.90us

12

ompt_target_data_transfer_from_device | 250.76us |

6.91% I

11

250.76us

250.76us 1

250.76us

13

ompt target submit intel | 155.04us |

4.27% 1

11

155.04us | 155.04us | 155.04us |

14

[...]

15

Total |

3.63ms | 100.00% |

11 1

16

17

BACKEND ZE | 1 Hostnames | 1 Processes | 1 Threads |

18

Name I

Time | Time(%) | Calls |

Average |

Min |

Max

19

zeModuleCreate | 846.26ms |

96.89% 1

1 1

846.26ms 1

846.26ms 1

846.26ms

20

zeCommandListAppendMemorvCopy | 10.73ms |

1.23% 1

12 | 893.82us | 12.96us |

5.33ms

\overline{21}

[...]

22

Total | 873.46ms | 100.00% |

117 I

23

24

Device profiling | 1 Hostnames | 1 Processes | 1 Threads | 1 Devices |

25

Time | Time(%) | Calls | Average |

Name |

Min |

Max

26

zeMemorvCopv(DM) |

64.48us

7.14% |

1 | 64.48us |

64.48us |

64.48us

27

omp offloading 33 7d35e996 MAIN 19 | 27.84us |

3.08% |

1 | 27.84us | 27.84us | 27.84us

28

[...]

29

Total | 902.72us | 100.00% |

13 I

```

| 1663919851.2 s + 1                                                                      | 73 s | 1 | +22.1 ms | +72.1 ms | +122.1 ms       | +172.1 ms | +222.1 ms | +272.1 ms     | +322.1 ms | +372.1 ms | +422.1 ms     | +472.1 ms  | +522.1 ms | +572.1 ms      | +622.1 ms    | +672.1 ms |

|-----------------------------------------------------------------------------------------|------|---|----------|----------|-----------------|-----------|-----------|---------------|-----------|-----------|---------------|------------|-----------|----------------|--------------|-----------|

| ×                                                                                       |      |   |          |          |                 |           |           |               |           |           |               |            |           |                |              |           |

| <ul> <li>exaperf-sdpcloud-pvc11.jf.intel.com<br/>Device 1   uuid 3</li> </ul>           |      |   |          |          |                 |           |           |               |           |           |               |            |           |                |              |           |

| exaperf-sdpcloud-pvc11.jf.intel.com  <br>Device 1 Luuid 3                               |      |   |          |          |                 |           |           |               |           |           |               |            |           |                |              |           |

| zeCommandQueue 1                                                                        |      |   |          | 2        | eMemoryCopy     | MD)       | zeM       | emoryCopy(M   | D)        | ze        | MemoryCopy    | (DM)       | 1         | zeMemory       | Copy(DM)     |           |

| zeCommandQueue 2                                                                        |      |   |          |          |                 |           |           |               | z         |           |               |            |           |                |              |           |

| <ul> <li>exaperf-sdpcloud-pvc11.jf.intel.com</li> <li>Process 31496   uuid 1</li> </ul> |      |   |          |          |                 |           |           |               |           |           |               |            |           |                |              |           |

| exaperf-sdpcloud-pvc11.jf.intel.com  <br>Process 31496 Luuid 1                          |      |   |          |          |                 |           |           |               |           |           |               |            |           |                |              |           |

| Thread 31496                                                                            |      |   |          |          | pt_target_data_ |           | . ompt_ta | rget_data_tra |           |           | t_data_transf | er_from_de |           | _target_data_t |              |           |

|                                                                                         |      |   |          | zeM zeO  | CommandQueue    | Sync Zem. | zeComm    | andQueueSyr   | ichro     | zecomr    | nandQueueSy   | nchronize  |           | CommandQu      | eueSynchroni | ze        |

Building an Hip Runtime: One example

- LLVM OpenMP is build on top of HSA

- SYCL is build on top of L0

- Can we build Hip on top of LO?

> A quine is a computer program which takes no input and produces a copy of its own source code as its only output.

>>> c = 'c = %r; print(c %% c)'; print(c % c)

c = 'c = %r; print(c %% c)'; print(c % c)

Multi-quine

(https://github.com/rvantonder/pentaquine/tree/master/src):

- 1 \$ python pentaquine.py py | diff pentaquine.py -2 \$ python pentaquine.py cc > pentaquine.c ; cc pentaquine.c 4 (pentaquine cc | diff pentaquine c

- 3 \$ ./pentaquine cc | diff pentaquine.c -

- 4 \$ ./pentaquine py | diff pentaquine.py -

- $\cdot\,$  As a proof of concept lets see how can we mimic Allocate Host

- Real ECP project ChipStart lead by Brice Videau https://github.com/CHIP-SPV/chipStar

- $\cdot$  In real life, far more complicated. (see source code for more fun)

1 hipError\_t hipMallocHost( void \*\*ptr, size\_t size) ^^I^^I

Level Zero Equivalent

- - $\cdot\,$  Hip implicit initializes and terminates the runtime. Not the case for  ${\rm L0^{40}}$

- Hip has no explicit concept or device<sup>41</sup>

<sup>40</sup>And HSA, and cuda driver

<sup>41</sup>State machine :(, like Cuda Driver

- Singleton to initialize the level zero runtime<sup>42</sup>

- Replicate the HIP state-machine: Create a default context, with a default device<sup>43</sup>

- $\cdot\,$  Use this context and device to allocate memory  $^{44}$

<sup>42</sup>What about race conditions in multi-threaded?

<sup>43</sup>Or all the devices?

<sup>44</sup>Alignment? Option to pass to *ze\_device\_mem\_alloc\_desc\_t*?

#### zeInit Real World Related Example: SYCL Runtime LO Backend

- 1 // We must only initialize the driver once, even if urPlatformGet() is called

- 2 // multiple times. Declaring the return value as "static" ensures it's only

- 3 // called once.

- 4 static ze\_result\_t ZeResult = ZE\_CALL\_NOCHECK(zeInit, (0));

Since C++ 11 also check std::call\_once and once\_flag

- Nothing is impossible

- $\cdot$  Can always climb up or down the abstraction ladder

- $\cdot\,$  Hip on top of Level Zero is a valid path

# Conclusion

- Layers of Programming Model<sup>45</sup>

- Sharing some common concept (loading kernel, async commands, nd-range, queue/stream)

- You may want to use High-Level Language (OpenMP, Kokkos, SYCL) and use interopt to lower-level (L0, Cuda Driver, HSA) if required

- Trace, play with the runtime!<sup>46</sup>

<sup>45</sup>Soon to be a complete graph<sup>46</sup>And on Intel Platform, just email me

## Q&A