## Introduction to GPU "Low-level" Programming

How does that even work?

Thomas Applencourt, Nathan Nichols ({apl,nnichols}@anl.gov) July 28, 2025

#### Disclaimer

- "If it's simple, it's always false. If it's not, it's unusable." Paul Valéry

- · "Trust, but verify." Russian proverb

- "Stay awhile and listen..." Deckard Cain 1

<sup>&</sup>lt;sup>1</sup>And sorry in advance for the 2h long lecture

#### ToC

- 1. Introduction

- 2. Programming Model for the GPUs Kernel

- 3. Execution Model

- 4. Programming Model API / Runtime

- 5. Summary

- 6. Example and Q&A

Introduction

#### Non-Goals of this lecture

- I will not teach you CUDA<sup>2</sup>, HIP<sup>3</sup>, Level Zero<sup>4</sup>

- You are all smart, if you need to learn it you can find super nice tutorial online

<sup>&</sup>lt;sup>4</sup>But maybe I will teach you some OpenCL – Open Compute Language...

<sup>&</sup>lt;sup>2</sup>Compute Unified Device Architecture,

<sup>&</sup>lt;sup>3</sup>Heterogeneous-Compute Interface

## Goal of this Lecture: How This code is Implemented

OpenMP<sup>5,6</sup>

```

#pragma omp target parallel for map(to: B[0:N]) map(from: A[0:N])

for (int i=0; i < N; i++)

A[i] = B[i];</pre>

```

I'm going to ask someone at the end, so listen carefully!

<sup>&</sup>lt;sup>6</sup>I use OpenMP – as example because after me, you have the chance, the privilege!, to get a OpenMP tutorial. But same goes for Kokkos, SYCL, Python

<sup>&</sup>lt;sup>5</sup>Open Multi-Processing... Wait what?!

#### Goal of this Lecture

- Give you some foundation to understand the difference and similitude between multiple low-level programming models ("Any fool can know. The point is to understand." Ernest Kinoy)

- Make clear the layering approach of current toolchains

## Some big questions

Why the "need" to use CUDA for NVIDIA hardware, HIP for AMD, and LO for Intel?<sup>7</sup>

(a) Level Zero

(b) CUDA

**(c)** HIP

<sup>&</sup>lt;sup>7</sup>But then how can OpenCL be portable?

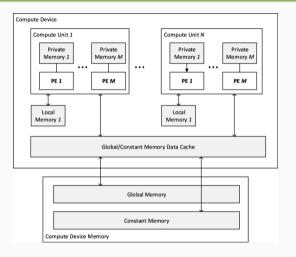

## GPU-programming consist on three things:

- Programming Model for the GPUs Kernel (OpenCL C, CUDA C, ...).

- Execution Model (SPMD / "MPI-like")

- Programming Model for the "CPU Runtime" (CUDA, L0, OpenCL)<sup>8</sup>

<sup>&</sup>lt;sup>8</sup>This is the only thing who matter, this rest is trivial

Programming Model for the GPUs Kernel

#### GPU is a different Hardware

- GPU Doesn't execute the same machine code as your CPU

- You need and additional compiler<sup>9</sup> to lower your high-level language to GPU machine code

<sup>&</sup>lt;sup>9</sup>or compiler backend

## Old School: Double Source Approach

#### - Host Code:

Written in C/C++/Python for CPU tasks like memory management and kernel launches.

#### - Device Code:

- Written in GPU-specific languages like CUDA C/C++, HIP C, or OpenCL C<sup>10</sup>

- Contains the GPU kernels.

<sup>&</sup>lt;sup>10</sup> PTX, SPIR-V, ...

#### **GPU** program

```

// CUDA/HIP

extern __shared__ float array[];

__global__ void cuda_or_hip_hello() {

printf("Hello World from GPU!\n");

}

// OpenCL

__kernel void hello_world() {

printf("Hello World from GPU!\n");

local int a;

}

```

#### So much difference!

- Please note the \_\_global\_\_, or \_\_kernel, those are not standard C keyword.

- What can you put in device code has limitation depending on the Hardware / Compiler

- · No dynamic allocation, no throw, no recursion, no virtual Functions, ...

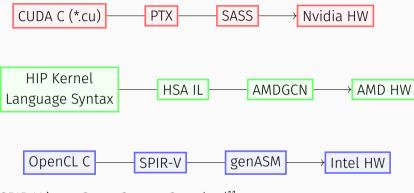

## Compiling: Simple first steps

SPIR-V is an Open-Source Standard<sup>11</sup>

<sup>&</sup>lt;sup>11</sup>The other are not, just saying

## Compiling: Simple first steps

SPIR-V is an Open-Source Standard<sup>12</sup>

<sup>&</sup>lt;sup>12</sup>The others are not, just saying

### **Double Source Compilation Process**

- · Separate Compilation:

- · Host code -> x86/ARM machine code.

- Device code -> Intermediate code (PTX, SPIR-V) -> GPU-specific machine code.

- **Potentially Linking**: Combines host and device code into the final executable (see next slide single source).

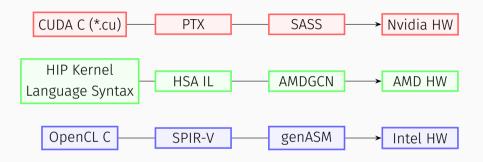

## Hiding Compilation: Emergence of Single Source

Compiler is smart enough to understand which code will be executed on the CPU, and which one on the GPU.

• You can use a subset of C/C++/Python as a GPU kernel<sup>13</sup>

<sup>&</sup>lt;sup>13</sup>Remember previous limitation: no recursion\*, no exceptions, no syscall, no io...

## Compiling: A Better(?) method – LLVM example

(you have bridge between SPIR-V and PTX)

<sup>&</sup>lt;sup>14</sup>or nobody generate AMDGCN and everybody HSA IL, not clear...

#### Recap

- Two compilation path, always

- · Can do it at runtime (JIT) or at compile time (AOT)

- GPU is fast, because it's stupid and have restriction

**Execution Model**

Kernel Language: GPU programming 101

**Execution Model**

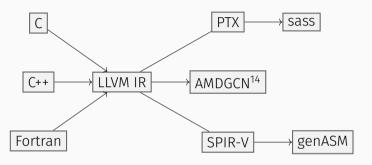

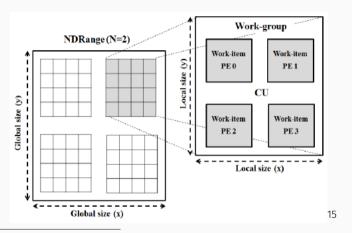

## Memory Hierarchy in GPUs

#### Overview of GPU Memory Architecture

- · Compute Device:

- Comprises multiple **Compute Units** (CU), each containing several **Processing Elements** (PE).

- Private Memory:

- Dedicated to each PE, storing element-specific data.

- Local Memory:

- · Shared among PEs within the same CU, facilitating intra-unit communication.

- Global/Constant Memory:

- Global Memory: Large, accessible by all PEs, used for cross-CU data sharing.

- · Constant Memory: Read-only, stores constants and configuration data.

- Memory Caches:

- Intermediate cache layers improve access times for frequently used data.

## **GPU Memory Architecture**

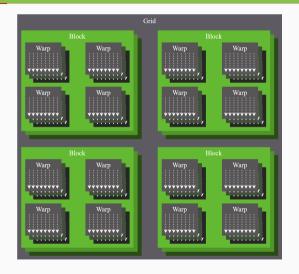

## **Execution Hierarchy: CUDA**

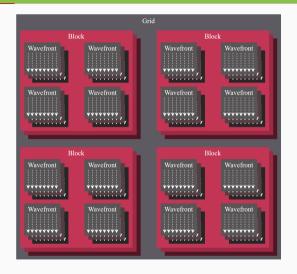

### **Execution Hierarchy: HIP**

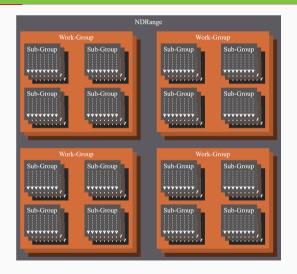

## **Execution Hierarchy: OpenCL**

## **Execution Hierarchy in GPU Programming**

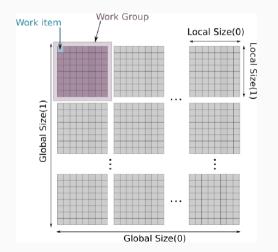

#### · NDRange/Grid:

- Defines the total computation space as a grid of threads.

- · Specifies the overall dimensions and workload size.

#### Work-Group/Block:

- Divides the NDRange into manageable chunks.

- Each work-group operates independently, using shared local memory.

#### · Sub-Group/Warp/Wavefront:

- · Smaller units within a work-group that execute in lockstep.

- Optimize data sharing and access patterns within the group.

#### Work-Items/Threads:

- · The fundamental execution units in a GPU.

- Each thread has private resources and can access shared local memory.

## Key Points to Understanding the Execution Hierarchy

#### · Efficient Parallelism:

- Optimize work-group sizes for load balancing.

- · Prevent resource underutilization with proper grid/block sizing.

#### Data Locality:

- · Maximize shared memory usage to reduce global memory access.

- · Align data structures with hardware capabilities.

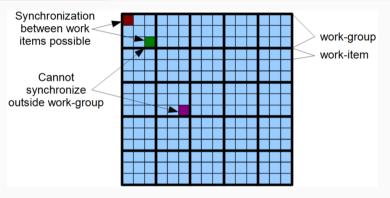

#### · Synchronization:

- Use synchronization within work-groups to manage dependencies.

- · Minimize unnecessary synchronization to avoid bottlenecks.

#### Memory Access Patterns:

- · Coalesced memory access enhances efficiency.

- Optimize data layout for better performance.

#### · Scalability:

• Design for scalability across different GPU architectures.

• Ensure kernels can adapt to varying numbers of compute units.

## Launching Kernel

$<sup>^{15}\</sup>mathrm{From}$  "Design of OpenCL Framework for Embedded Multi-core Processors"

## **Index Space**

From "An Introduction to the OpenCL Programming Model" by Jonathan A. Thompson

## Synchronization Possibilities

From An Introduction to the OpenCL Programming Model by Jonathan A. Thompson

Implementing atomic synchronization mechanisms is an advanced topic

#### **GPU** in a Nutshell

- Just think of the GPU as a CPU with lots of threads executing SIMD instruction

- GPU cannot allocate memory

- GPU programs are pretty boring:

- Use Shared Local Memory<sup>16</sup> when possible to not read from the Main Memory

- Be careful of register pressure

- "Nothing Special" memory access<sup>17</sup>

- GPU are fast because they force you to NOT synchronize between threads that live in difference work-group. Freedom versus Performance.

- · No branch prediction

<sup>&</sup>lt;sup>16</sup>Shared Memory in CUDA, or just rely on cache oblivious algorithm

<sup>&</sup>lt;sup>17</sup>"coalescing memory" == Don't do random access / gather. "vectorization" strategies: contiguous versus strided access.

Programming Model API / Runtime

# Programming Model API / Runtime

**Runtime and Runtimes**

## Just a layer of Programming Model / Runtime!

"All problems in computer science can be solved by another level of indirection." David Wheeler

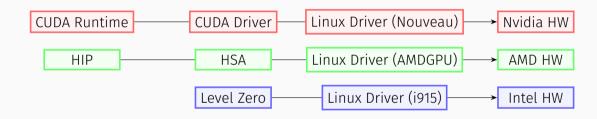

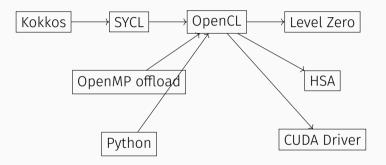

## Proprietary / Native Tool-chains (put Python Anywhere you like)

# Comments on this diagram

- The Linux Drivers are the "lower-level" we will discuss. Huge effort to implement.<sup>18</sup>

- The level on top (CUDA Driver, HSA, Level Zero) abstracts away a little bit more of the hardware, but still provides a lot of control <sup>19</sup>

- The last level (CUDA Runtime, HIP) are "fully" hardware independent

<sup>&</sup>lt;sup>18</sup>See nice blog post about the Linux M4 drivers

<sup>&</sup>lt;sup>19</sup>Sweet spot to write higher-lever runtime

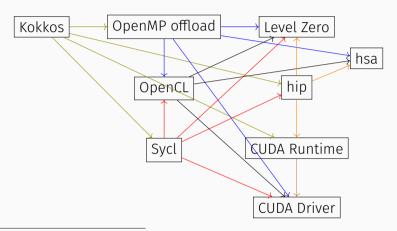

# Taking About Higher-level Programming Model<sup>20</sup>

<sup>&</sup>lt;sup>20</sup>Where is my Vulkan! Sorry gamer people... And thanks Valve for Direct3D -> Vulkan

# Example of Paths

- OpenCL -> \*21

- · OpenMP Offload -> HSA

- Kokkos -> CUDA Runtime -> CUDA Driver

- · HIP -> CUDA

- HIP, CUDA -> L0<sup>22</sup>

<sup>&</sup>lt;sup>21</sup>Yes, I Like OpenCL... Soon you will too!

<sup>&</sup>lt;sup>22</sup>Maybe more surprising, we will talk about this more at the end if we have time and interested

# Hierarchy of Programming Model

- In short we have a "High Level" programming model. Used by Application.

- · A "low-level" programming model that the high-level runtime is written with

- Each layer of abstraction is a trade-off between flexibility/performance and convenience/productivity

All of this is **relative** to who you are talking with.

### "Sad" Truth

- · No technical reason for having so much "intermediate" programming model

- · hipcc was a perl script that did 's/cu/hip/g' to avoid copyright infringement<sup>23</sup>

- Always hard to have a standard (\*insert XKCD\*)

- OpenCL is the standard, but low-adoption by vendors

- Please don't let vendors make the same mistake with new ML accelerators!

<sup>&</sup>lt;sup>23</sup>Not a lawyer, but the "recent" supreme court Google vs Oracle may help

# **Controversial Opinion**

HIP and CUDA Runtime should not be used anymore.

- Too low-level for Applications that want to use nice C++ construct<sup>24</sup>

- Too high-level for people who have advance use-cases.

Kokkos, SYCL, OpenMP Offload already bypass HIP / CUDA runtime, so no "overhead" by using those programming models

<sup>&</sup>lt;sup>24</sup>Come on, who wants to cast the output of malloc...

# My Dream World

You are young and not yet totally jaded, so I share my dream with you!

Programming Model API / Runtime

Main concepts (shared)

# Side note: They all have good old C API<sup>25</sup>

```

// Get number of platorm

cl_uint platformCount;

clGetPlatformIDs(0, NULL, &platformCount);

cl_platform_id* platforms = malloc(sizeof(cl_platform_id) * platformCount);

// Populate the newly allocated array

clGetPlatformIDs(platformCount, platforms, NULL);

```

<sup>&</sup>lt;sup>25</sup>I Don't check error code, because I'm not that of a great programmer...

### What are a GPU Runtime's Main Goals?

- 1. Find devices

- 2. Load/Compile your kernels

- 3. Create Queue / Steam

- 4. Allocate GPU Memory

- 5. Execute commands (data-transfer, kernels)

- 6. Synchronize

Not that hard! Tedious but Simple<sup>26</sup>

<sup>&</sup>lt;sup>26</sup>If only everything was like this...

# Device. Easy

```

// OpenCL

cl int clGetDeviceIDs(

cl platform id platform.

3

cl device type device type.

cl uint num entries.

5

cl device id* devices,

cl uint* num devices):

// Level Zero

ze result t zeDeviceGet(ze driver handle t hDriver.

9

uint32 t *pCount.

10

ze device handle t *phDevices)

11

// Cuda Driver

12

CUresult cuDeviceGetCount ( int* count )

CUresult cuDeviceGet ( CUdevice* device. int ordinal)

// Cuda Runtime

15

cudaError t cudaGetDeviceCount ( int* count )

16

cudaError t cudaGetDevice ( int* device )

17

```

## Queue / Stream

- Device are "explicit" / "separate object" / considered as accelerator.

- Queue/Stream<sup>27</sup> are the concept/object used to dispatch work to the device.

<sup>&</sup>lt;sup>27</sup>Trivia, difference between queue and stream? Spoiler, answers on the next slide

# Differences between programming models

- In L0, queues are out-of-order by default<sup>28</sup>

- In CUDA runtime and driver and HIP, streams are in-order<sup>29</sup>

- In OpenCL, they can be both

- In HSA, it's a ring buffer of packets

### Out of order, you said?

- Out-of-order, mean kernel is free to re-order kernel execution... and concurrent execution is a re-ordering!

- · Can be a source of error (and poor performance if not used)

<sup>&</sup>lt;sup>29</sup>For more complex use cases, use cuda-graph

<sup>&</sup>lt;sup>28</sup>The latest LO version we know have a ZE\_COMMAND\_QUEUE\_FLAG\_IN\_ORDER flags.

# Queue / Stream: What to Submit?

Submit "command" to queue/stream. Commands can be

- · Kernel Submission

- Memory Copy

- · Synchronization (fence, barrier, event...)

- ...

# Loading/Creating GPU Kernel

- Your code was split between hosts and GPU code (as we showed)

- Your kernels need to loaded by the GPU runtime!

```

clCreateProgramWithSource

clCreateProgramWithIL

clCreateProgramWithBinary

zeModuleCreate ( ZE_MODULE_FORMAT_IL_SPIRV | ZE_MODULE_FORMAT_NATIVE)

cuModuleLoad

```

#### **Command Submission**

On bad API (but convenient to use), commands can be submitted blocking manner

```

CUresult cuMemcpy ( CUdeviceptr dst, CUdeviceptr src, size_t ByteCount ) // Where is my stream?!

```

On good one they asynchronously by default

# Hammering Down on the Async Concept

- Asynchronous execution just mean the CPU is free to continue to do other thing (like submitting other kernel). The call is not blocking / synchronous.

- The fact that the GPU can potentially execute multiple command concurrently is conceptually orthogonal to async. 30

- Async mean you need to explicit synchronize, and handle dependency between commands.

<sup>&</sup>lt;sup>30</sup>One Can use multiple MPI process, or Multiple Thread, ...

# **Command Submission Tips**

- · Async is a common source of error

- Blocking is a common source of poor performance

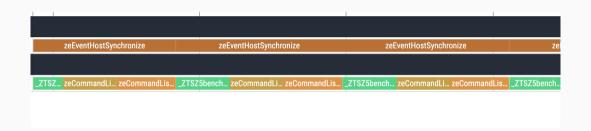

# Synchronization: Event / Barrier

If it's asynchronous... you need to synchronize (insert "D'oh!" homer meme)

- · via Event (specify dependencies for fine grained synchronization)

- via Barrier (for coarse synchronization)

#### Fine Grained: Event

```

OpenCL. L0<sup>31</sup>:

zeCommandListAppendMemoryCopy(..., &e1) // e1 will be signaled at completion

zeCommandListAppendMemoryCopy(..., &e2) // e2 will be signaled at completion

zeCommandListAppendMemoryCopy(..., 2, {e1,e2}, &e3) // wait for e1 and e2, e3 will

→ be signaled at completion

zeEventHostSynchronize(e3) // And then finaly synchronization the leaf

CUDA, Hip:

hipMemcpvAsvnc // Hip. Cuda have optional Asvnc. default blocking

hipEventRecord

hipEventSvnchronize

(for more fancy use cases, use cuda-graph)

<sup>31</sup>So elegant

```

#### Coarse Grain: Barrier

Wait on queue / stream (wait until all the work has been done)

- zeCommandQueueSynchronize

- 2 cudaStreamSynchronize

- cudaDeviceSynchronize // Whoa? Don't do that

Coarse grain. Use with caution because too much synchronization is bad.

# Programming Model API / Runtime

Notes on Performance

# Async is Key to good performance

- · You want to keep the GPU busy

- When the GPU is computing something, the CPU should start preparing the next batch of work

- Importance of asynchronously

Async: [OpenMP][AMDGPU] Switch host-device memory copy to asynchronous version (real thing: https://reviews.llvm.org/D115279)

# Overlapping is Key to good performance

- PCI is damn slow!<sup>32</sup>

- PCI 64 GB/s (unidirectional)

- · HBM 1 TB/s

- GPU 50 TFlops+33

- · Recompute is better than to load

- · Overlap compute and data-transfers

- PCI is bidirectional so please do H2D and D2H at the same time!

- · Avoid over-synchronization!

<sup>&</sup>lt;sup>32</sup>And for integrated architectures, you have NUMA so same things... Data-movement will always be more expensive than compute

<sup>&</sup>lt;sup>33</sup>And a few billions times more if you believe nvdia marketing slide and fantasy math

# So how to achieve concurrency?

# Importance of asynchronously!<sup>34</sup>

- Extract Maximum parallelism opportunity from your apps (this is the really hard part)

- · Submit kernels to multiple stream / queue

- · Submit kernels to an out-of-order queue.

- · Synchronize: Not too much, not too little, just right.

<sup>&</sup>lt;sup>34</sup>Or use multiple thread / process but this is cheating

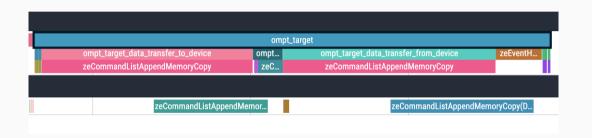

# Example

- · 3 Independent Kernel To submits (D2H, Kernel, H2D)

- You can imagine as computing current iteration, moving back data of previous iteration, prefetching data for the next iteration

# Example: Vibe-coded Bad

# Example: Vibe-coded Bad-Problem, solution

Gap in the timeline... And too much synchronization!

#### Solution:

- Use Async API, so with some luck your command will be long enough that you can submit new one in the meantime.

- Stop Synchronize too much

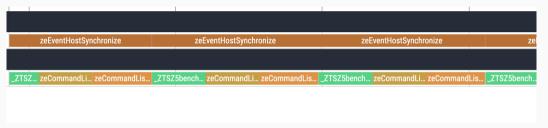

# Example: Bad Blocking

# Example: Bad Blocking

All kernel serialized. Not that Bad gpu utilization but we can do better. (the code is using In-order queue).

Solution: Extract more concurrency from your code! Out-of-order queue, or more multiple in-order queues.

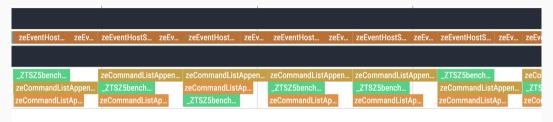

# Example: Good

Amazing Concurrency of Kernel, H2D, and D2H (3x buy using a out-of-order queue)

(The picture is more zoomed-in, and maybe misleading; the runtime of the apps is 3 times faster)

**Memory Allocation**

Programming Model API / Runtime

# Types of GPU Memory<sup>38</sup>

- Device Memory: Accessible only on the particular device<sup>35</sup>

- · Shared Memory: Accessible by both the host and the device<sup>36</sup>

- This may impact performance, Different migration strategies

- · Can be migrated via prefetching<sup>37</sup>

- Host memory

- "Pinned" memory. CPU memory but has been registered by the runtime.

- $\boldsymbol{\cdot}$  May required for some optimizations / performance

- Malloc-ed Memory

$<sup>^{35}\</sup>mbox{Read}$  the documentation to know if it's accessible by OTHER devices. Context, wink, wink

<sup>&</sup>lt;sup>36</sup>Nvidia calls it "Managed"

<sup>&</sup>lt;sup>37</sup>Do not confuse with prefetch of memory inside a kernel

<sup>&</sup>lt;sup>38</sup>OpenCL has buffer, but lets not go that way...

# But future GPUs will be integrated!

- · Doesn't matter,

- NUMA is bad, Locality is good.

- · Please don't use shared everywhere...

### Best Case Scenario

- · All data fit on the GPU

- · Move everything over

- · Do a ton of computation

- · Move back results

You should aim for this. If you cannot, we will discuss other strategies latter.<sup>39</sup>. **Memory transfers are expensive. Don't do it!** Or at least try...

<sup>&</sup>lt;sup>39</sup>Please not that it's the same in CPU. Keep data in cache

Programming Model API / Runtime

**Kernel Submission**

#### Kernel: CUDA Runtime / HIP

Magic / Syntactic sugar<sup>40</sup>

mykernel<<<br/>blocks, threads, shared\_mem, stream>>>(args);

But that just call HSA / Cuda Driver behind the scenes.

<sup>&</sup>lt;sup>40</sup>A new syntax just to avoid people being portable...

#### Behind the seen: OpenCL, CUDA

```

cl int clEnqueueNDRangeKernel(cl command queue command queue,

cl kernel kernel.

cl uint work dim.

const size t *global work offset.

const size t *global work size.

const size t *local work size.

cl uint num events in wait list.

const cl event *event wait list,

cl event *event)

9

10

CUresult cuLaunchKernel ( CUfunction f, unsigned int gridDimX, unsigned int

11

gridDimY, unsigned int gridDimZ, unsigned int blockDimX, unsigned int

blockDimY, unsigned int blockDimZ, unsigned int sharedMemBytes, CUstream

→ hStream. void** kernelParams. void** extra )

```

#### Behind the seen: Level zero, HSA

```

// Similar in L0, Count versus Size, and by kernel

2

zeKernelSetGroupSize(hKernel, groupSizeX, 1, 1);

ze group count t groupCount = { numGroupsX, 1, 1 };

zeCommandListAppendLaunchKernel(hCommandList, hKernel, &groupCount, NULL, 0,

→ NULL):

6

// HSA you get a packet from queue and then signaling, but still same idea

typedef struct hsa kernel dispatch packet s { uint16 t header :

uint16 t setup:

uint16_t workgroup_size_x ; uint16_t workgroup_size_y ; uint16_t workgroup_size_z;

10

→ uint16 t reserved0:

11

uint32 t grid size x ;

uint32_t grid_size_y ;

12

uint32 t grid size z:

13

uint32_t private_segment_size; uint32_t group_segment_size;

14

15

```

# Programming Model API / Runtime

\_\_\_\_

Recap of those section

## Summary of Runtime

- · HIP, CUDA (runtime, driver), LO kind of all the same

- Always: "Discrete" device, load kernel, submit command async, synchronize. If not, it's just abstracted away

- Push your vendor/institution/PI to use a standard (OpenCL).

- DON'T WRITE YOUR OWN PORTABILITY LAYER! (pretty please)41

<sup>&</sup>lt;sup>41</sup>Just use SYCL...

### **Summary**

- You see, all the programming model are same. And lot of Bridge between them!

- · Create Kernel, Queue, Execution, Synchronize

- Some are less verbose more high level (HIP/CUDA runtime) but you lose some flexibility<sup>42</sup>

- IMO HIP/CUDA runtime are in a weird intermediate level and should never be used.

<sup>&</sup>lt;sup>42</sup>And need to deal with some state-machine...

#### But does this matter? This sounds trivial

#### Real Time Experience (controversial)

- Experience: The runtime performance is far more important than the kernel performance

- Improving Kernel performance will give you a few percent; doing too much data-transfer will slowdown your code 100x.

#### Conclusion

- GPUs do not have the same ISA as CPU, so two compilation phases

- GPU are fast because they are simple  $\rightarrow$  they are just a big SIMD 10k+ threads CPU

- Lots of good tutorials online for GPU Kernel Programming

**Summary**

#### Summary

- · OpenCL, L0, Cuda Driver -> All The same

- · C API. "Double source" (CPU and Accelerator sources).

- Create queue, Kernel Creation, Submission Command, Synchronization Host

GPU

- · Thinks of GPU are SIMD Machine

- All GPU the same

- Abstraction are powerful.

# Example and Q&A

# OpenMP: Now tell me what it does

```

#pragma omp target parallel for map(to: B[0:N]) map(from: A[0:N])

for (int i=0; i < N; i++)

A[i] = B[i];</pre>

```

#### **Proof**

Any questions? If not I will show you some code...